TMS320C6455入门实践(三)

本系列文章链接

- TMS320C6455入门实践(一)——编译CSL静态库

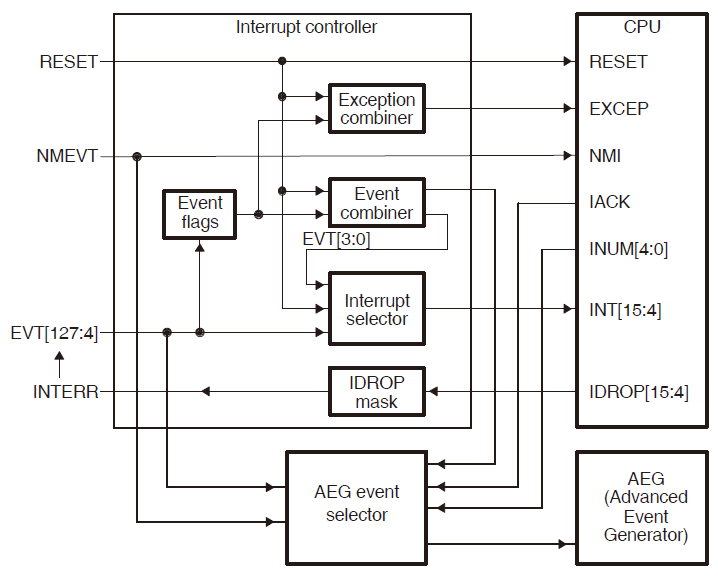

- TMS320C6455入门实践(二)——中断相关

- TMS320C6455入门实践(三)——PLL相关

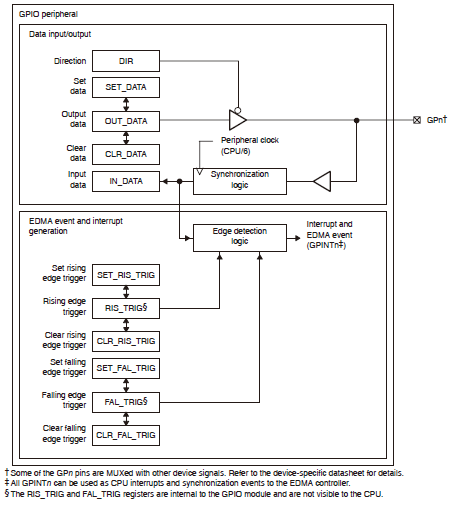

- TMS320C6455入门实践(四)——GPIO与定时器

- TMS320C6455入门实践(五)——cmd链接脚本

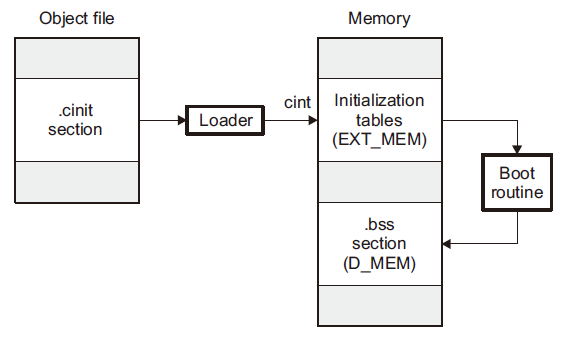

- TMS320C6455入门实践(六)——编写boot程序

- TMS320C6455入门实践(七)——生成启动镜像

- TMS320C6455入门实践(八)——Flash驱动与程序固化

- TMS320C6455入门实践(九)——DDR上运行代码

- TMS320C6455入门实践(十)——EDMA3相关

本文主要介绍TMS320C6455的时钟相关的内容,参考文档为:

- SPRS276M - TMS320C6455 Fixed-Point Digital Signal Processor

- SPRUE56 - TMS320C645x DSP Software-Programmable Phase-Locked Loop (PLL) Controller

C6455有两个PLL,PLL1输出的时钟用于大部分外设,PLL2输出的时钟专门用于DDR2控制器和以太网媒体访问器(EMAC)。

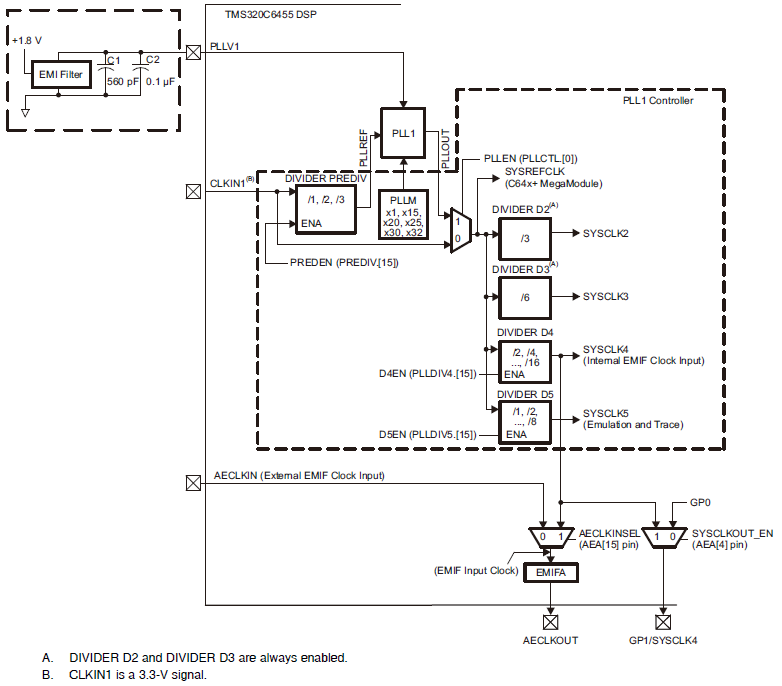

PLL1和PLL1控制器

PLL1相关的框图如下图所示。从框图上看,整个PLL1控制器是虚线框里的部分,包括一个预分频器、一个二选一的多路选择器和四个分频器,另外可以通过PLLM配置PLL1的倍频系数。

SYSREFCLK就是系统的主频。

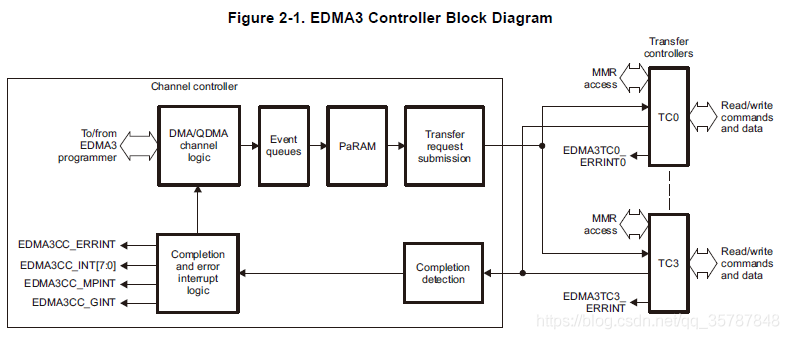

SYSCLK2固定为主频的三分频,用于驱动Switched Central Resources(SCRs)、EDMA3、VCP2、TCP2和RapidIO,还有EMIFA和DDR2的数据总线。

SYSCLK3固定为主频的六分频,主要用于驱动PCI、HPI、UTOPIA、McBSP、GPIO、TIMER和I2C外设。

SYSCLK4的分频系数可以在一定范围内设置,主要作为EMIFA的内部时钟。

SYSCLK5的分频系数也可以在一定范围内设置,主要用于在线仿真。

系统复位之后PLL1控制寄存器中的PLLEN值为0,PLL1被旁路,因此复位后的系统时钟即为输入的时钟信号的频率。因此每次复位后都需要对PLL1重新进行配置,才可以保证系统工作在较高的工作频率。

在调试过程中,因为我们只能对PLL的控制器进行操作,所以如果系统不掉电,PLL1的状态会保持前一次配置的结果。比如在第一次下板调试时,我对PLL1做了一次配置;而在不断电的情况下,我又重新载入新的程序,而不对PLL1做配置,那么PLL1还是会保持前一次程序中的设置结果。

与之相关的寄存器配置也很简单,无非就是一些使能和倍频、分频系数的控制。设置完成后,通过PLLCMD寄存器中的GOCMD字段写入“1”来确认配置,当PLLSTAT寄存器中的GOSTAT字段变为“0”时,表示配置完成。

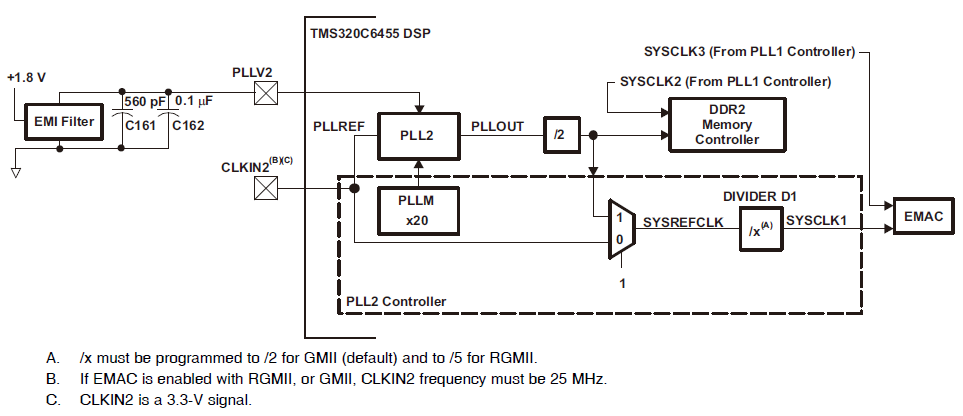

PLL2和PLL2控制器

PLL2的结构比PLL1更加简单,下图就是PLL2的框图。别看图中有个多路选择器,其实仔细看会发现它的控制端始终是1,所以它的输出始终是来自PLL2产生的时钟。

PLL2固定20倍频,然后输出再二分频,所以总共就是十倍频。参考时钟如果是25MHz,那么在系统复位后,送给DDR2控制器的时钟以及SYSREFCLK都是250MHz。

PLL2能够控制的就只是D1的分配系数,以及D1的使能。默认D1为二分频且上电就使能,用户可以通过PLLDIV1来修改,使其禁用或者改为五分频。

CSL的使用

- CSL_pllcInit()没有什么实际的作用。

- CSL_pllcOpen()用于指定具体要用的PLLc,PLL1的控制器或者PLL2的控制器。

- CSL_pllcHwSetup()根据CSL_PllcHwSetup的配置结构体进行配置。

- 然后用CSL_pllcGetHwStatus()查询GOSTAT,等待配置完成即可。