输入输出延时的时序约束

关于FPGA设计时的输入延时、输出延时的基本概念,网上已经有很多文章进行了介绍。

文章链接:FPGA静态时序分析

我主要也是通过上面这篇文章进行学习的。但是文章中对于最大输入延时的推导有一点小错误,而且整体上看比较复杂,为此本文进行了适当总结。

在很多文章的分析中,常常引入时钟抖动(jitter),时钟偏斜(skew),因此常常会显得比较复杂。为了便于分析,时钟的这部分不确定性我们可以暂时不考虑,即把发射(launch)和捕获(capture)的时钟看作完全相同的时钟。

建立时间与保持时间

在讨论输入输出延时之前,一定要对建立时间和保持时间有足够的理解。

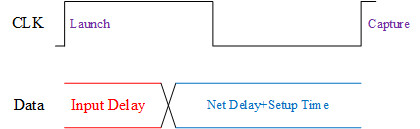

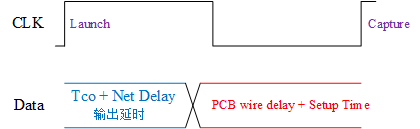

- 建立时间是否满足,需要考虑发射沿和捕获沿之间的关系,是前后两个时钟沿。从发射沿开始,经过一定的延时,数据在捕获端稳定。在捕获沿到来前,数据至少要稳定一定的时间,这一段时间称为建立时间。

- 保持时间是否满足可以仅考虑捕获沿,即同一个时钟沿。捕获端在捕获数据时,数据需要保持一段时间,而有可能因为发射端数据来得太快导致保持时间不满足。

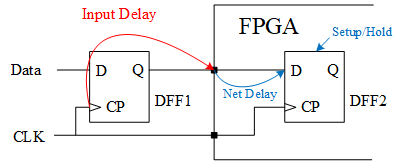

输入延时

输入延时即图中红色弧线表示,DFF1的时钟端到FPGA的PAD的时间。具体包括DFF1的Tco和PCB走线延时。

输入延时会有一个范围,即最大输入延时和最小输入延时,明确这两个限制有什么用呢?

最大输入延时

考虑最大输入延时,如果这个延时越来越大,会造成什么后果?可能会造成DFF2因为建立时间无法满足导致无法采到输入的数据。

因此一个最大输入延时的约束,实际上是对DFF2的建立时间和图中的Net Delay之和进行了限制。建立时间和线网的延时之和不能太大。

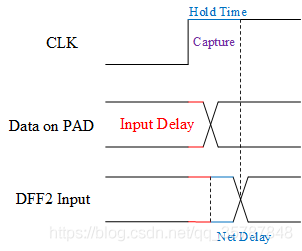

最小输入延时

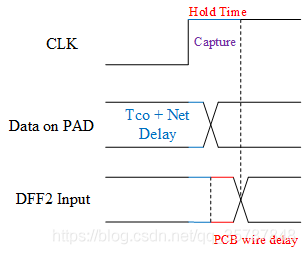

同样考虑最小输入延时,如果这个输入延时特别小,会造成什么后果?输入延时很小的话,对满足建立时间自然是非常有利的,但是会对满足保持时间提出更高的要求。因为输入延时如果太小,数据会更快地来到DFF2的输入端,很可能导致上一个数据的保持时间不满足。

图中红色线段表示输入延时,蓝色部分表示FPGA内部的Net Delay和Hold Time,当Input Delay非常小时,可能需要通过增加Net Delay来满足保持时间的要求。

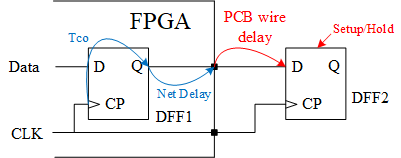

输出延时

输出延时包括两部分,如上图蓝色部分所示,一部分是输出寄存器的Tco,另一部分是寄存器输出后的Net Delay。

与输入延时不同,输入延时是人为设置的提供给FPGA设计工具的一个外部条件;而输出延时则是FPGA内的一个性质,我们需要给出外部条件,也就是给出PCB走线延时和捕获寄存器的建立时间与保持时间。FPGA设计工具会根据这些条件来调整输出延时。

最大输出延时

有个规律,关于这个最大或最小输入输出延时。凡是“最大”,都是通过建立时间得出的。

最大输出延时可以根据最大的PCB走线延时和捕获寄存器的建立时间得出,再结合时钟周期即可计算最大输出延时。因为输出延时如果更大,就有可能导致捕获寄存器的建立时间不能满足。

最小输出延时

最小输出延时同样根据捕获寄存器的保持时间来得出。最小输出延时是最小的PCB走线延时减去捕获寄存器的保持时间。可以从图中看出,这一计算结果有可能是负值,而这部分负值则需要FPGA的输出延时来提供。

比如我们计算得到的PCB走线延时减去保持时间是“-2ns”,那么Tco + Net Delay就需要至少为2ns才可以满足捕获寄存器的保持时间要求。

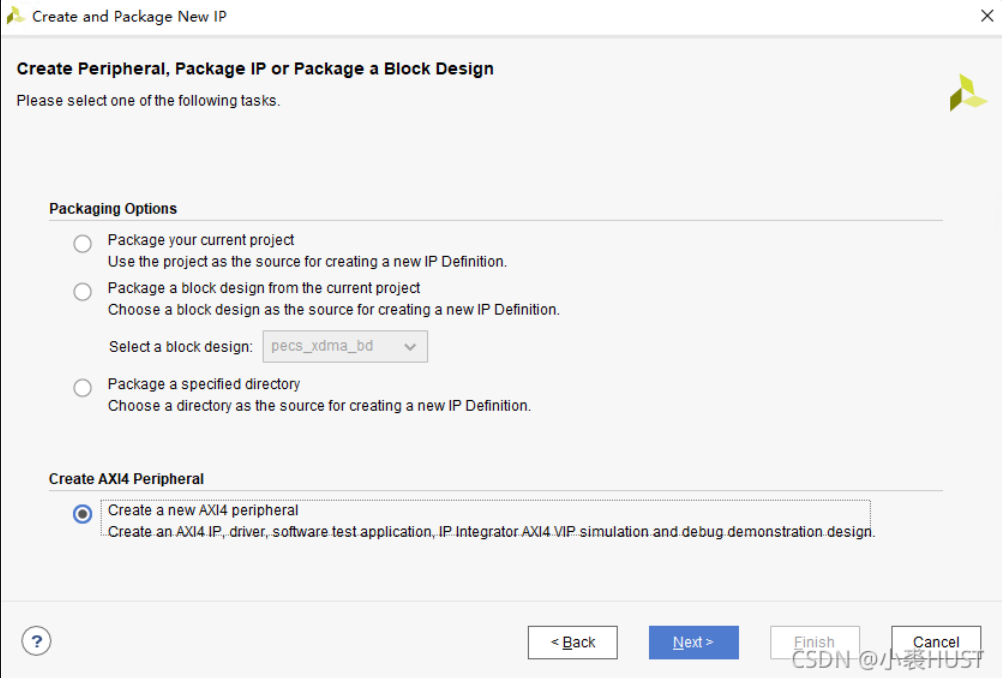

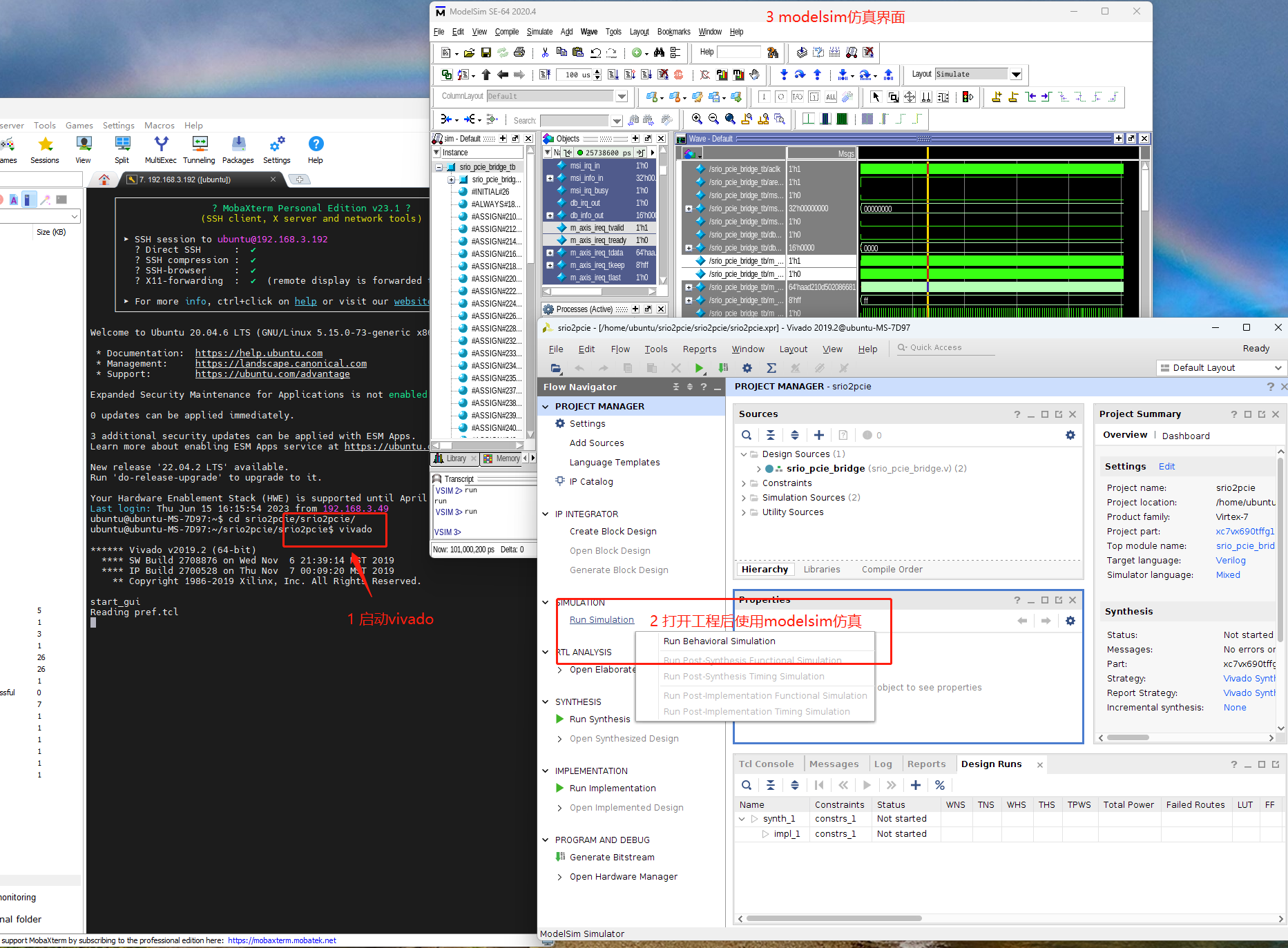

Vivado时序约束

在vivado里添加关于输出延时的时序约束,我一般都用那个Constraints Wizard。不管是在Synthesized Design里还是在Implementation Design里都有这个功能。

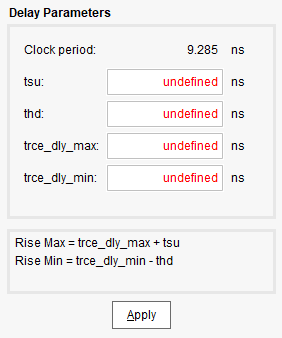

在关于输出延时的设置里面,选择需要设置的信号后,右侧有输入框,如下图所示。

时钟周期时根据信号所在时钟域已经确定了的。下面的tsu(建立时间)和thd(保持时间)就是捕获寄存器的建立时间和保持时间。trce_dly_max和trce_dly_min就是PCB的线路延时最大值和最小值。

图中下方的计算公式也和我上面的分析相印证,在这里设置好之后保存至一个xdc文件,内容类似下面这样的

1 | set_output_delay -clock [get_clocks clk_fpga_1] -min -add_delay 0.000 [get_ports hs_0] |

这里有一点容易误导人,就是这里的设置最大输出延时,给的数字实际上是最大PCB走线延时加上捕获寄存器的建立时间。实际上输出延时是指FPGA内的Tco + Net Delay。只是FPGA设计工具可以根据我们设置的这个条件去推断最大输出延时,也就是

最大输出延时 = 时钟周期减去 - (最大PCB走线延时+捕获寄存器的建立时间)