基于PCIe的FPGA与DSP间高速数据传输测试

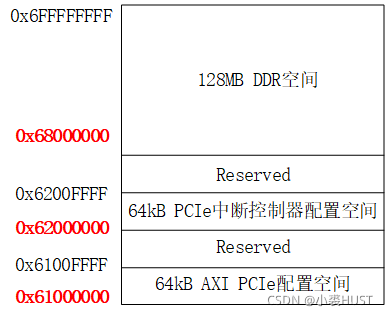

结合我前面两篇文章对FPGA和DSP两边的实现,本文对整个测试结果做一个总结。我用的FPGA和DSP都是国产的,对标Xilinx的XC7VX690T FPGA和TI的TMS320C6678 DSP。DSP作为RC,FPGA作为EP,实现DSP通过PCIe接口读写FPGA外接的DDR。

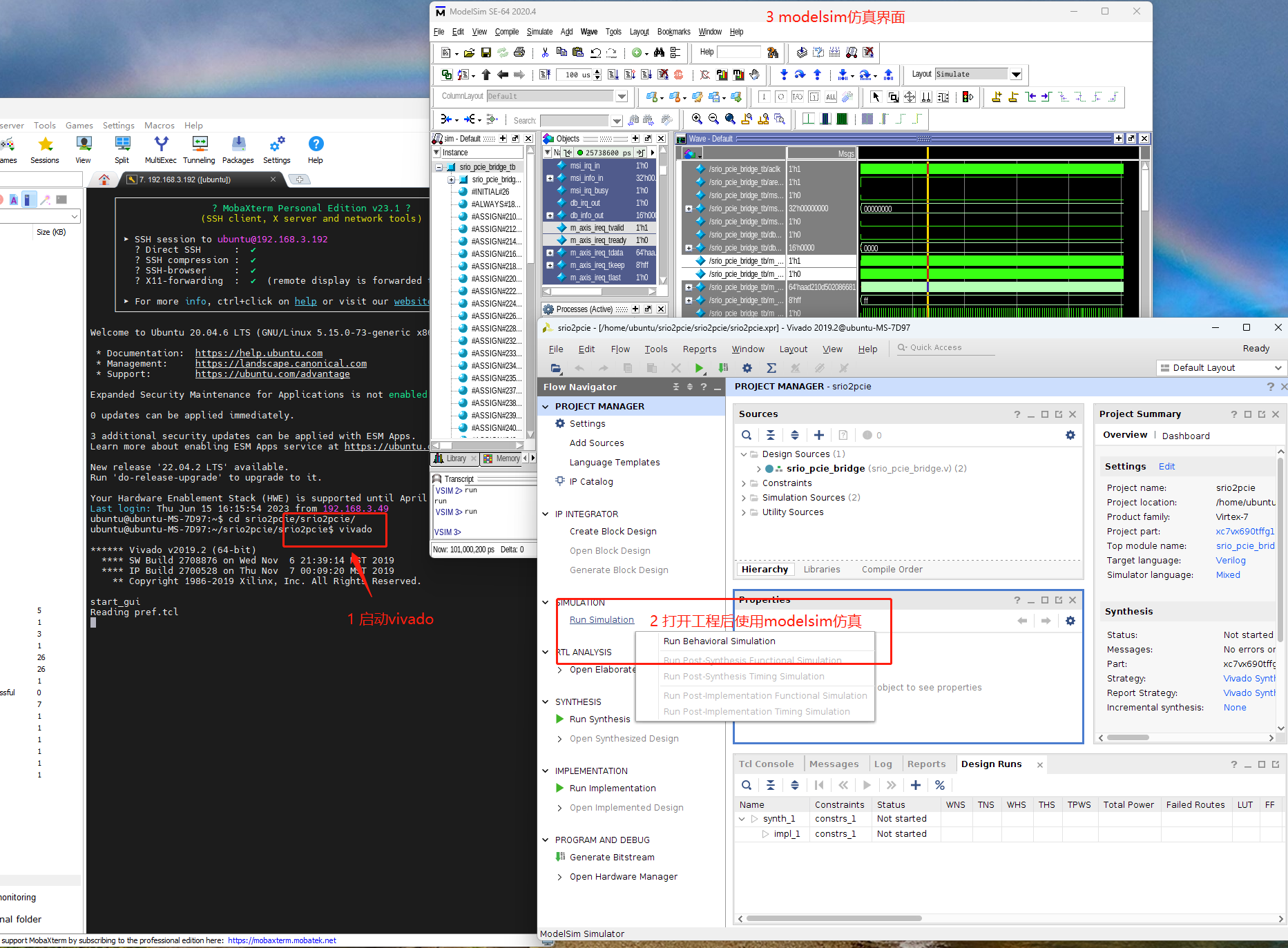

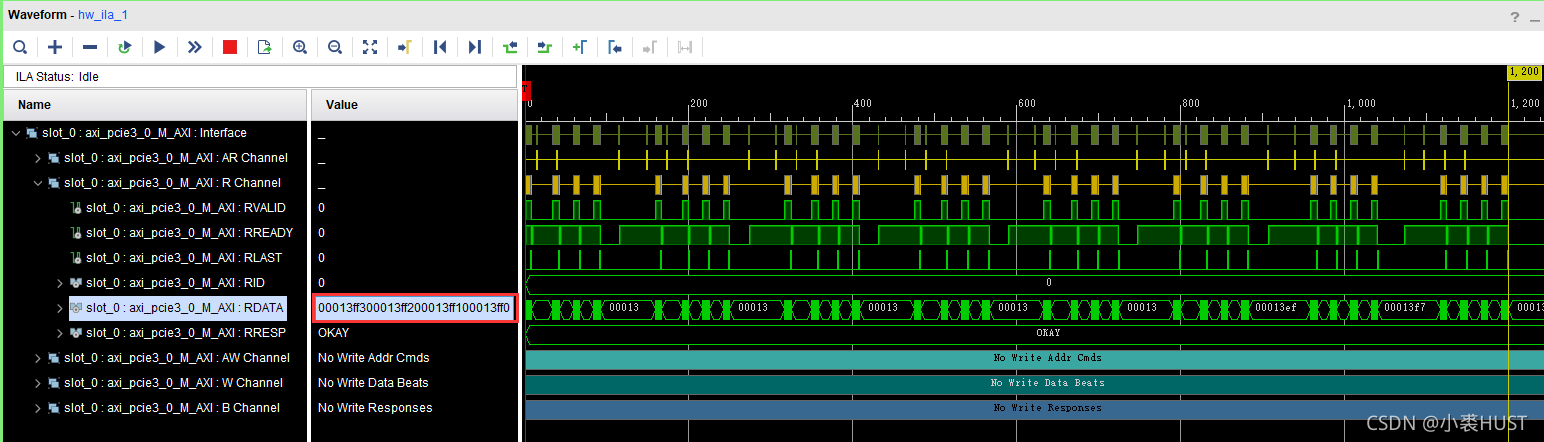

FPGA接口写时序图

总共的数据量是640×512×8bit,是一帧图像的大小。具体的数据是我生成的,不是真正的图像数据。DSP端这些数据是以字的方式存储的,一共有81920个字节,换算成16进制就是0x14000。下面的图是在PCIe IP的AXI接口处抓到的波形,可以看到最后一个写进去的数据是0x13FFF,说明数据都写进去了。

下面的图是详细的写数据的波形,数据位宽是16字节,突发长度是8。在数据最终写入DDR之后,返回成功的写响应。

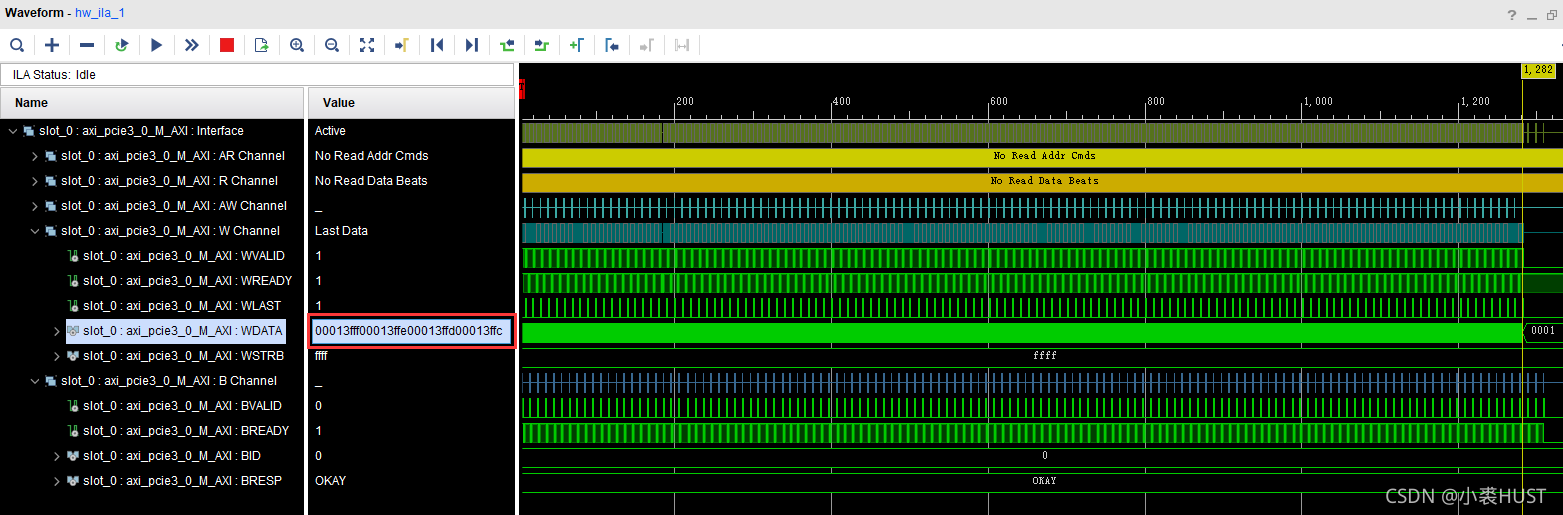

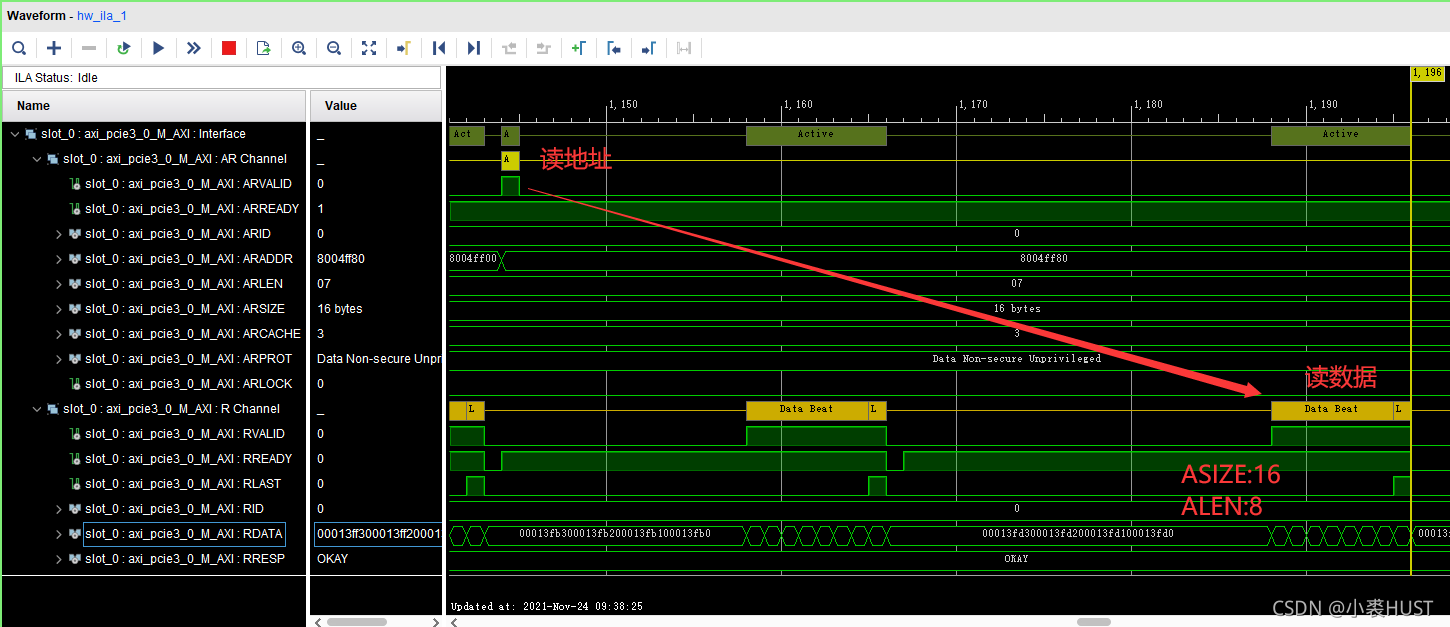

FPGA接口读时序图

下图是连续的读时序图,可以看到最后一个读出来的数据也是0x13FFF,所以读的数据也是没有问题的。

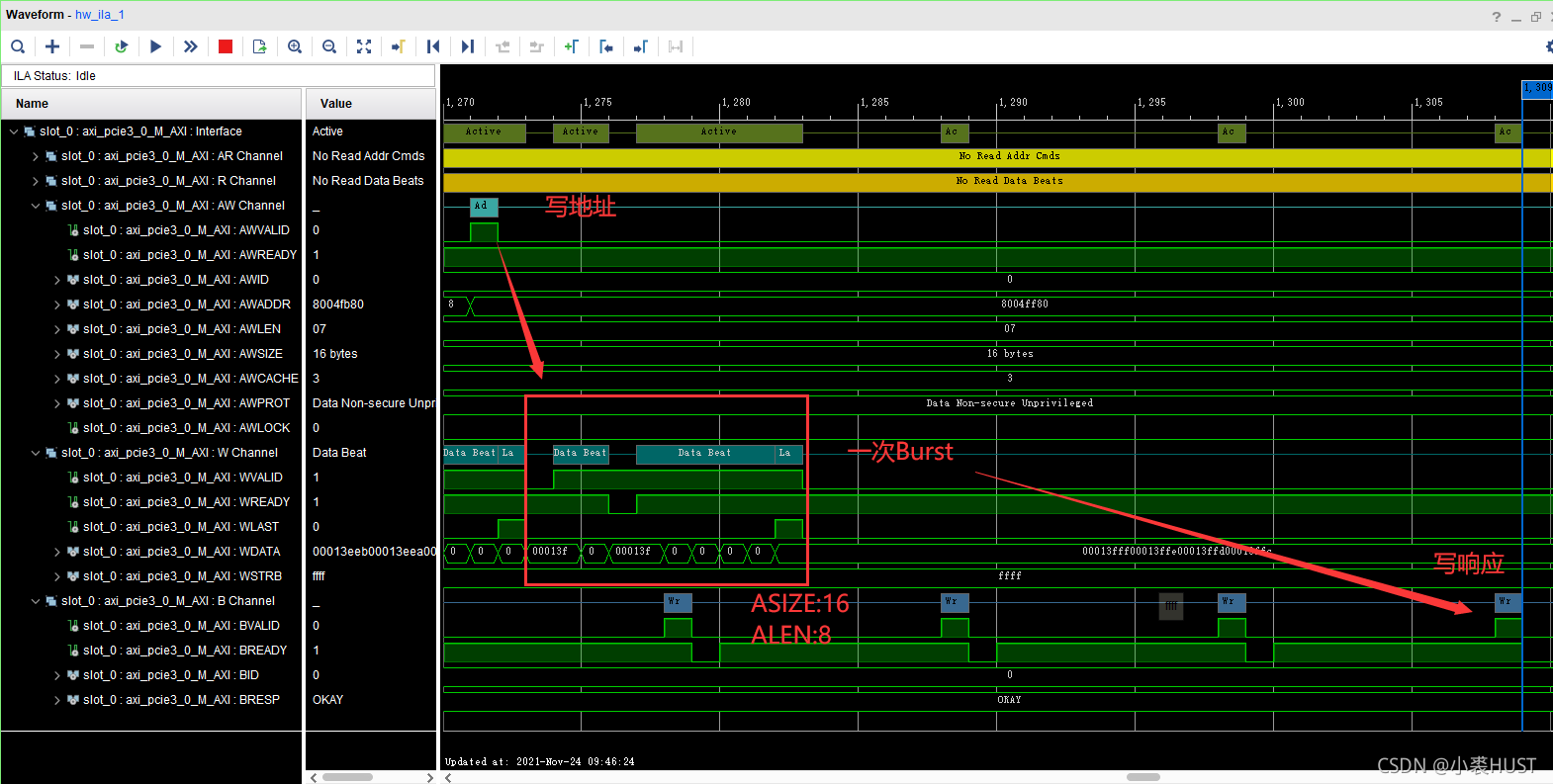

下面的图是详细的读数据的波形,可以看到在读地址的请求达到之后,过了一段时间有相应的读数据返回。每次读数据之间的间隔时间也比较长,这里的主要应该是访问DDR的时间限制了传输速率。

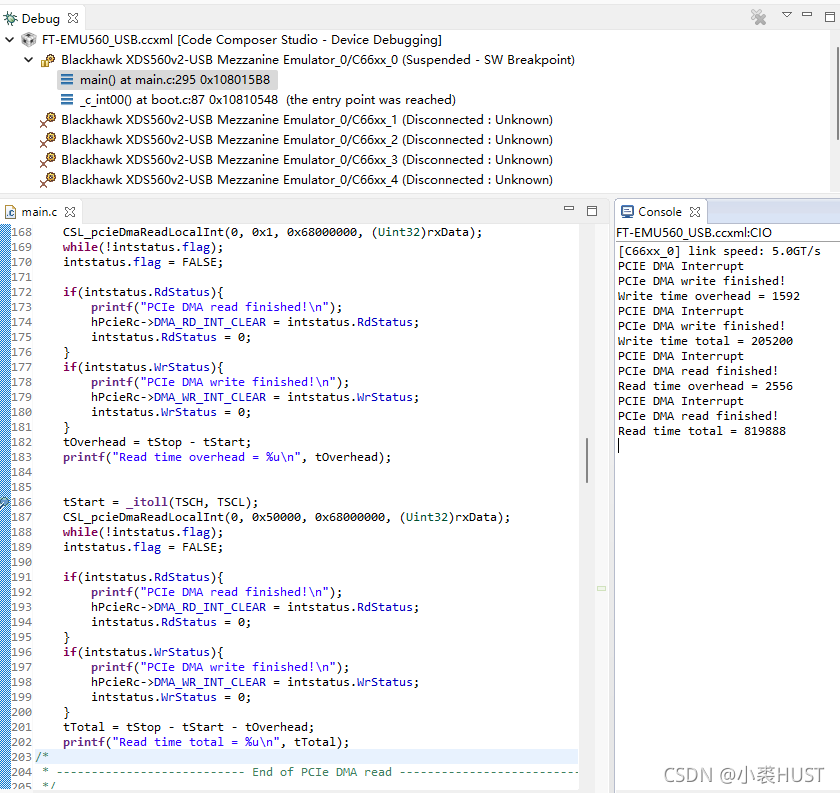

DSP PCIe DMA速率测试

上图是DSP端的传输速率测试结果。为了让测试的结果更加准确,在每次大批量数据传输之前我都先传1字节数据,用来计算一些函数调用、中断服务之类的额外开销,然后在后面的计时结果中减去这部分额外的时间。

PCIe DMA的有效写速率和有效带宽占比:

PCIe DMA的有效读速率和有效带宽占比:

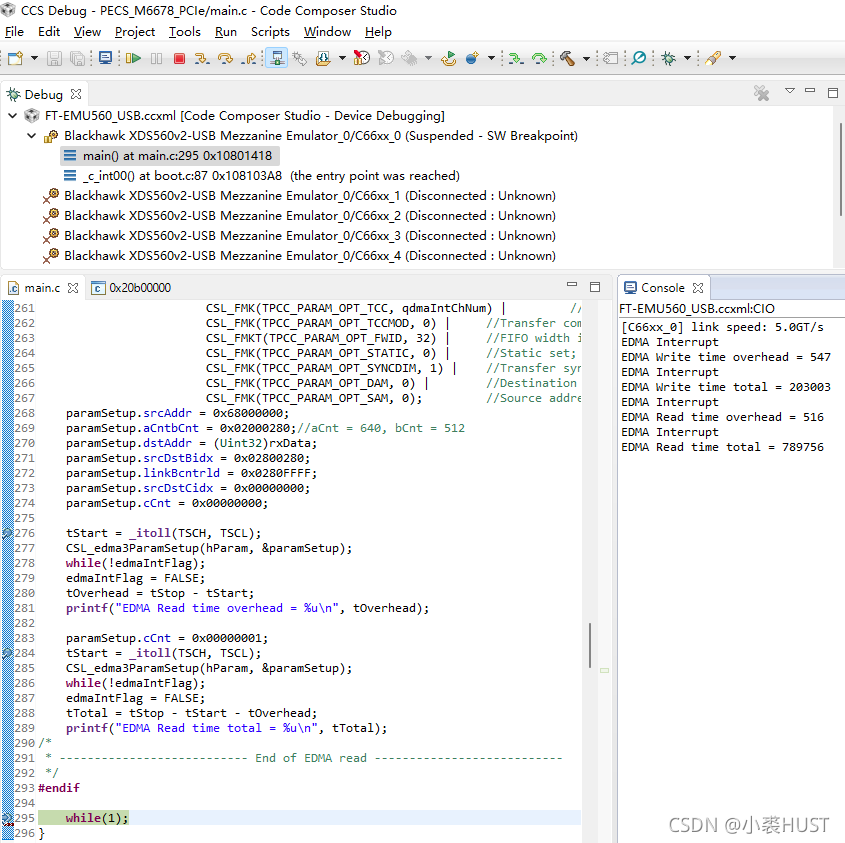

DSP EDMA速率测试

上图是利用EDMA进行读写测试,测试结果如下:

EDMA的有效写速率和有效带宽占比:

EDMA的有效读速率和有效带宽占比:

整体来说,EDMA和PCIe的DMA,传输速率都受到DDR的访问限制,因此两者的性能是非常接近的。但是EDMA更加灵活,所以我个人还是比较推荐用EDMA。

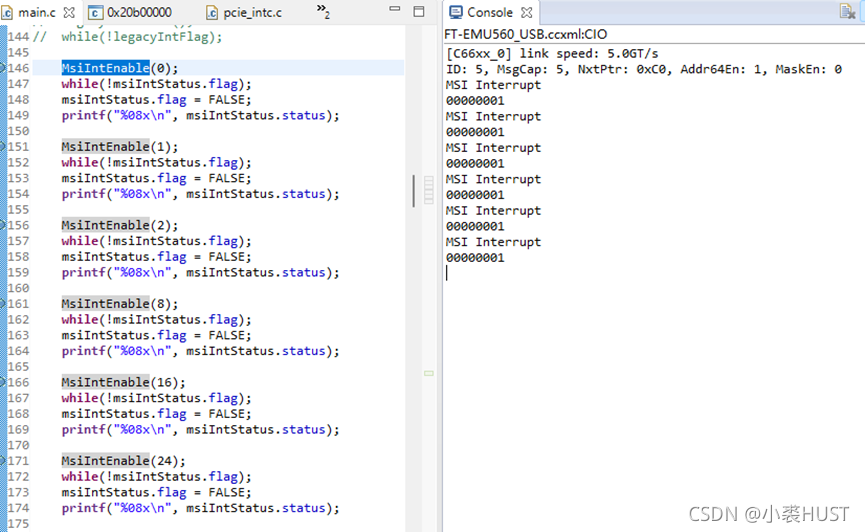

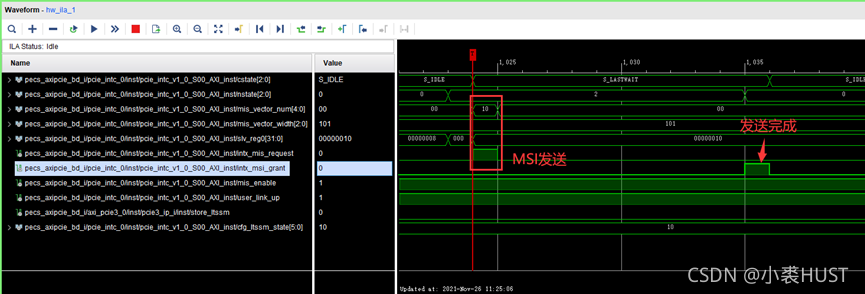

MSI中断

DSP的MSI中断就有点奇怪了。我做了一个简单的发送MSI中断的控制器,就是我前面提到的PCIe中断控制器。当DSP向它写入MSI中断向量号,并且将使能位置一之后,它就会通过PCIe发送指定的MSI中断。下图是它发送16号MSI中断的时序图。

DSP端确实是收到了MSI中断,但是跟文档描述的不符。文档说核0只能收到0、8、16、24号中断,但是我却也能收到1号和2号中断,查询MSI的中断向量号,结果都是0号MSI中断。只能说它实现了接收MSI中断的功能,但是无法区分不同的MSI中断。