DSP与FPGA的SRIO通信实现

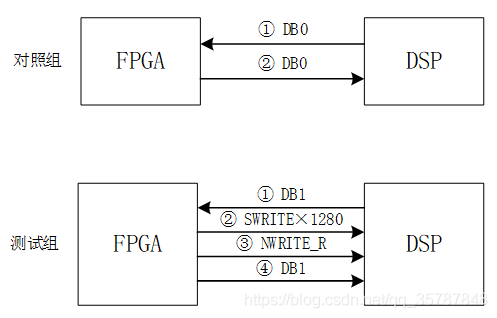

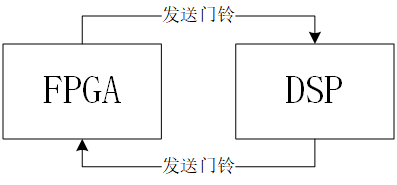

本文主要介绍在FPGA和DSP之间实现SRIO通信的过程。FPGA和DSP的型号分别为JFM7VX690T80-AS(XC7VX690T)和TMS320C6455。目前实现的是两者互相交替发送门铃事务,系统功能示意图如下图:

参考资料:

- SPRAA89A - TMS320C6455 Design Guide and Comparisons to TMS320TC6416T

- DS183 - Virtex‐7 T and XT FPGAs Data Sheet:DC and AC Switching Characteristics

- ANTC206 - Differential Clock Translation

- PG007 - Serial RapidIO Gen2 Endpoint v4.1 LogiCORE IP Product Guide

- SPRU976E - TMS320C645x DSP Serial RapidIO (SRIO)

硬件连接

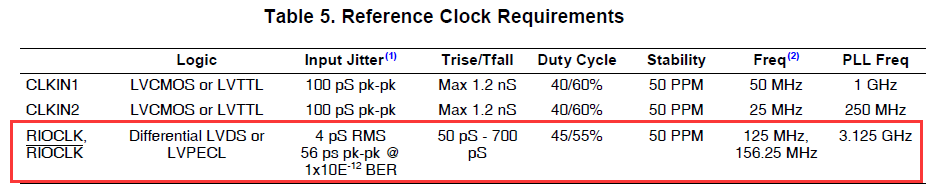

链路之间的连接采用100nF电容耦合,主要是不同的器件需要的时钟类型可能不同,需要注意。TMS320C6455需要采用LVDS或者LVPECL逻辑电平标准的差分时钟。而当时我们整个系统里的另一个处理器需要的是HCSL类型的时钟,两者不能直接兼容,需要在电路上做一些处理。

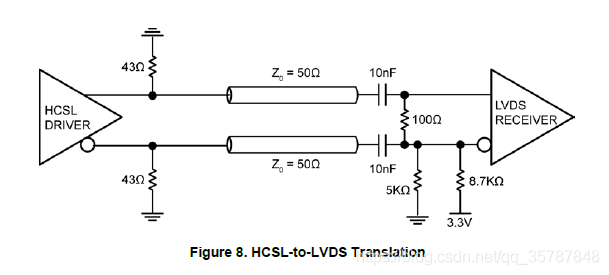

HCSL类型时钟转LVDS类型时钟,参考ANTC206,用的是下图中的电路。原理是另外引入3.3V,并用电阻分压,得到LVDS类型时钟的1.2V的共模电压,实际测试时发现,TMS320C6455的差分输入阻抗已经是100Ω,因此外面不需要再挂100Ω。

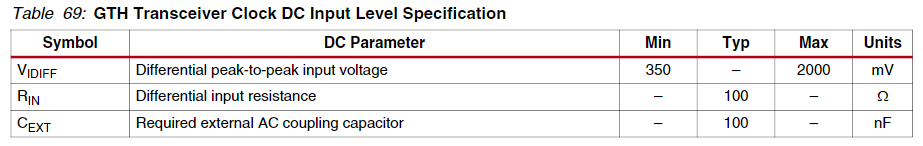

FPGA的GTX和GTH对参考时钟输入的电气要求比较松,只需要是电容耦合,并且差分电压的峰峰值在350mV~2000mV之间即可。HCSL类型的差分时钟电压峰峰值为1400mV(单端700mV),因此满足输入条件。

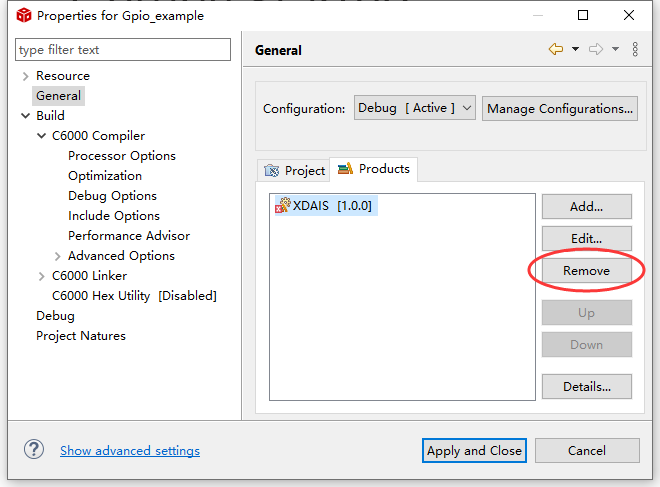

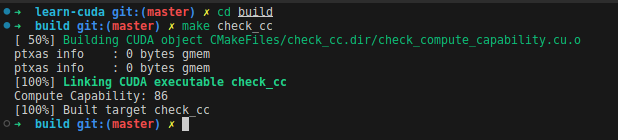

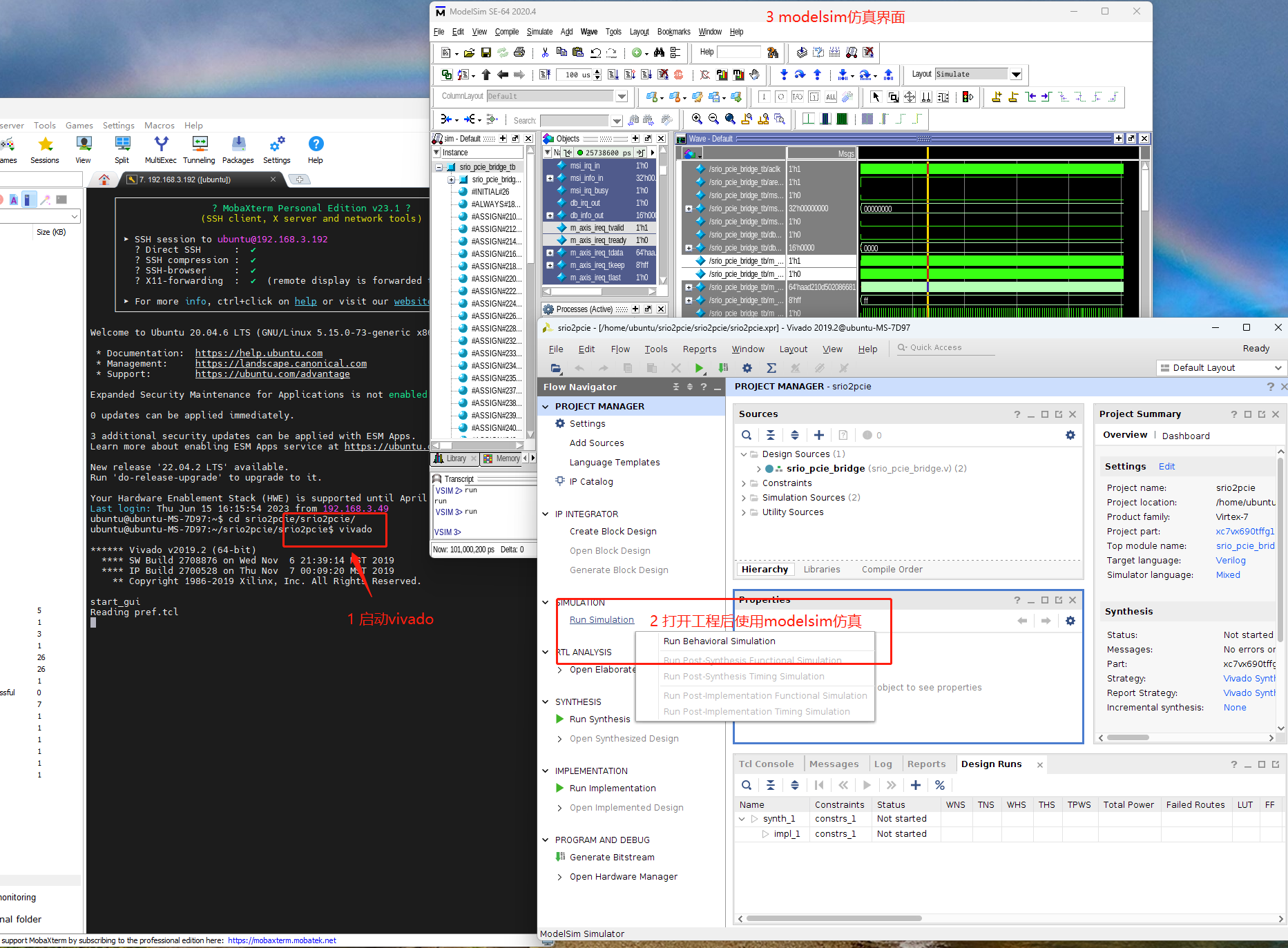

FPGA端实现

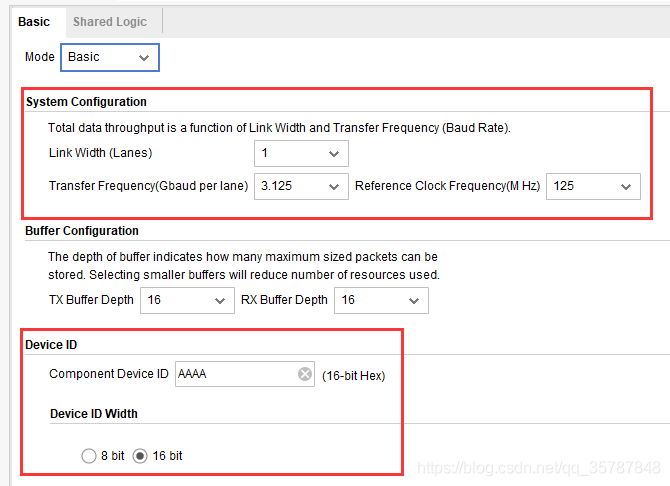

FPGA端实现SRIO主要参考PG007这个文档。SRIO的IP的配置可以很简单,主要就是把链路数量、链路的速率和参考时钟频率配置一下,记住它的Device ID即可。

IP实例化的时候,信号非常多,但是比较有用的就是四个AXI4-Stream端口,ireq,iresp,treq和tresp。用来发送和接收事务包。其余的都是IP的输出信号,方便观察调试,查找问题。下面是SRIO实例化代码的一部分,sys_clk是外部输入的参考时钟,IP能够输出log_clk给用户实现自己的逻辑。

1 | .sys_clkp(sys_clkp), // input wire sys_clkp |

- link_initialized和port_initialized指示链路和端口是否初始化完成

- deviceid就是我们在IP配置中设置的值,会用在事务包的发送和接收中。

- mode_1x指示当前工作在1x模式

- port_error,port_decode_error,gtrx_disperr_or,gtrx_notintable_or用来指示是否出现错误。具体错误信息可以查PG007。

1 | .sim_train_en(1'b0), // input wire sim_train_en |

另外有这四根线是输入,可以给常量。一开始我直接把仿真例程搬过来用的时候没有给sim_train_en置零,导致链路一直有问题。其余的输出信号都可以悬空,

还有一个我遇到的问题是,当时没注意到这个sys_rst是高电平复位,我直接把接了外部复位按键的Pin接到了sys_rst上,而电路上做的是低电平复位,导致没有按键按下的时候IP一直处在复位状态。所以这里对外部输入的复位取反(~sys_rst)。

FPGA的实现总体来说比较简单,就只要发送门铃后等待门铃,接收门铃的时候发送响应,再接着发送门铃就行。发送事务的过程都是通过AXI4-Steam的接口,基本不会有问题。

只是在工程最后输出bitstream文件的时候出了问题,提示需要购买license,参考这篇文章即可解决。

DSP端实现

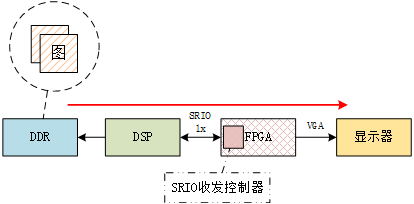

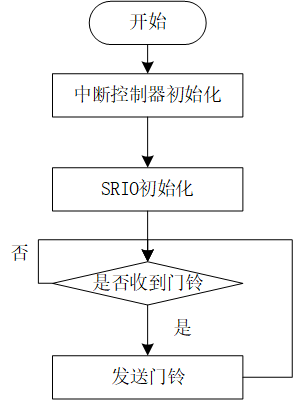

DSP端的软件流程图如下图所示。程序的编写和调试主要是参考SPRU976E。

初始化

从SRIO的初始化开始,只要能建立链路连接,就成功了一大半。

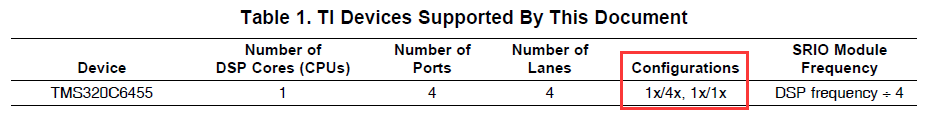

首先要弄清楚C6455的SRIO的工作模式。下面的表格里给出了它有两种工作模式。

- 1x/4x:工作在1条或者4条链路的模式,其中1条链路的情况下,可以是lane0或者lane2。也就是0~3四条链路中只有0和2两条链路作为单条链路进行通信;

- 1x/1x:只能工作在1x模式,就是四条链路都是独立的。

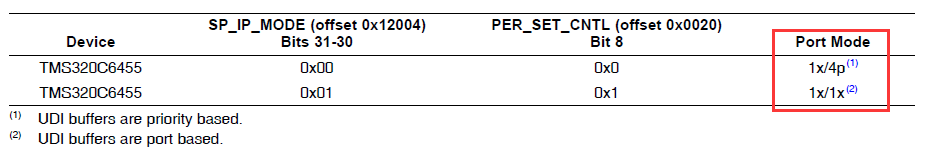

然后具体到代码配置过程中,下面的1x/4p让我误以为是4个端口都工作在1x模式,而实际上这里的1x/4p就是前面的1x/4x模式。我们的需求是把四条链路都独立使用,因此需要按照1x/1x的方式进行配置。

工作模式配置在PER_SET_CNTL寄存器中的BOOT_COMPLETE置一的时候就生效。就是当这一位置一时,C6455就开始对端口进行初始化。而后就不能再去修改工作模式了。CSL中自带的CSL_srioHwSetup函数上来就对BOOT_COMPLETE进行写入(写0或是写1取决于用户的配置)

一般情况下,如果直接写“1”,那么它就直接工作在1x/4x模式了;如果直接写“0”,那就是不起作用,同时可以对其它的寄存器做修改,如果想让其它的配置生效,就需要再写一次“1”,如此两次先后调用CSL_srioHwSetup才能将它的工作模式正确配置为1x/1x模式。

因此需要对这部分函数做修改,为此我将SRIO的配置分为两个阶段,一个是“预设置”,CSL_srioHwPresetup完成工作模式以及其他的一些配置;另一个CSL_srioFlowCtrlEnable是对BOOT_COMPLETE置一,并且在最后启动“流控制”(PCR寄存器中的PEREN需要最后置一)。

1 | CSL_srioHwPresetup(hSrio, &setup); |

如何判断是否初始化完成?可以通过SPn_ERR_STAT寄存器中的第1位,PORT_OK来判断。只有当PORT_OK为1时,端口之间的链路才建立起来。在调试过程中我发现通过CCS的“Registers”窗口看到的值和真实值是有区别的。我通过读取SPn_ERR_STAT寄存器中的数据,并打印到控制台上才发现虽然窗口中显示的没有变化,端口似乎还是没有初始化,但是读取数据之后打印的结果却是表明链路已经建立连接了。

1 | for(i = 0; i<4; i++){ |

如何判断当前链路工作在什么模式?可以通过SPn_CTL寄存器中的最高两位来判断,如果为“00”则表示当前这个端口是单链路的模式;如果为“01”,则当前是四条链路构成一个端口,而且只对于SP0_CTL有效。这里同样也会有类似上面的一样的毛病。就是CCS的Registers页面看到的值和实际值不符,需要打印输出才能看到正确的实际就结果。

1 | for(i = 0; i<4; i++){ |

一般只要配置没问题,这个链路就能建立起来。FPGA用ILA可以看到port_initialized和link_initialized都变高,DSP可以看到PORT_OK那一位置一就没问题了。

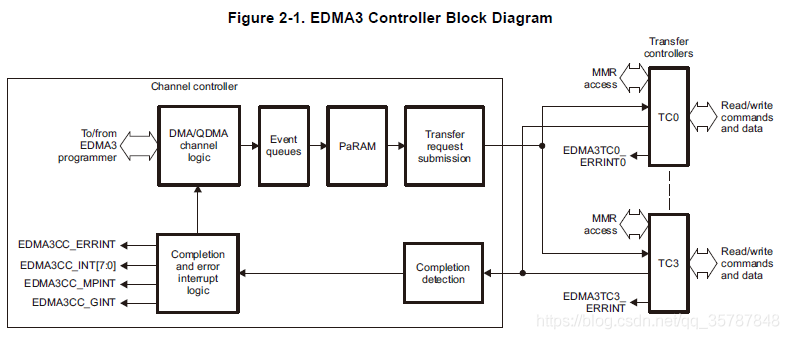

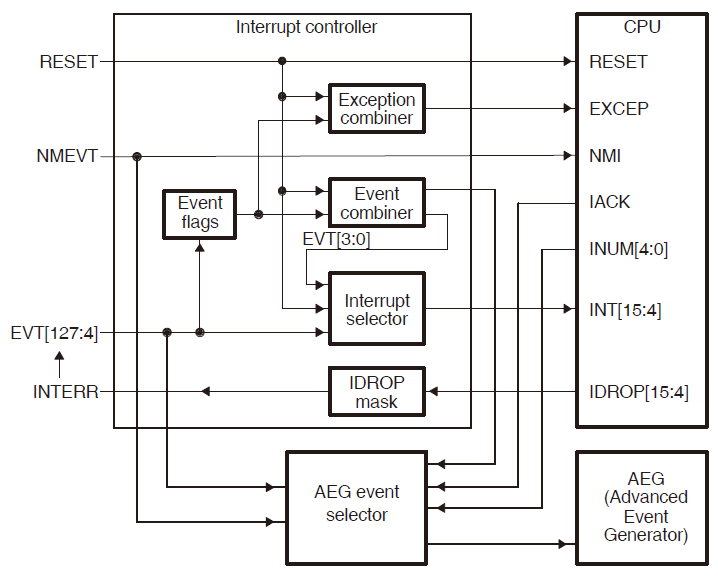

门铃中断

因为中断经常要用到,所以关于中断的配置这一块一定要非常熟悉才行。一个IntcObj把12个处理器中断源(VectID4~15)之一和128个Event之一联系起来,hIntc指向是IntcObj的指针。context和record是管理整个中断系统的全局变量,其中记录了所有中断服务函数的数量和函数地址。

初始化中断控制器,首先对context初始化赋值,调用CSL_intcInit即初始化了中断向量表,但这是中断服务函数都是空的。接着使能全局中断,使能不可屏蔽中断,以上操作在整个程序中只需执行一次。而后的CSL_intcOpen则是对单个中断源进行设置,如果系统中有多个中断源,则需要类似地执行多次。CSL_intcOpen初始化了IntcObj,将128个Event之一和12个CPU中断源之一联系在一起,本质上是修改了INTMUX寄存器。CSL_intcPlugEventHandler将中断服务函数和特定的中断联系在一起,最后再使能中断(实质上是将IER寄存器中的特定bit置一),即完成了中断的配置。

1 | CSL_IntcObj IntcObj; |

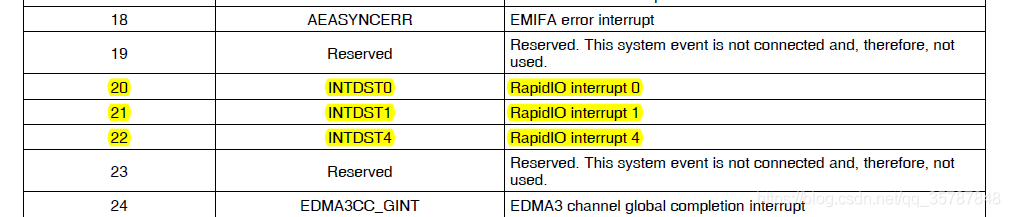

一般的中断配置流程就像上面说的那样,但是SRIO实际上有很多中断源,但分给它的只有3个Event(3/128),分别是INTDST0、INTDST1、INTDST4。所以实际上从门铃中断到Event还有一次映射。

这里需要配置SRIO的门铃的中断路由寄存器(ICRR),因为门铃共有64个中断源,这每个中断源都可以连接到以上三个Event之一,每次有中断发生时,用户可以通过查询的方式进一步确定发生中断的具体事件。为此,我专门写了CSL_srioDbIntrRoute函数,用于设置门铃的ICRR寄存器。而且由因为SRIO的寄存器只有在使能SRIO外设之后才能读写,所以这个函数需要在CSL_srioHwPresetup之后调用。

中断服务函数

1 | void Rio0InterruptHandler( |

以上是一个简单的中断服务函数,主要就是令flag自增1。每次中断产生时,有三处地方产生了中断标志,SRIO的ICSR,中断控制器的EVTFLAG和CPU的IFR。其中CPU的IFR会在每次中断服务函数被调用时自动清除,而另外两处中断标志则需要由软件手动清除。以上代码中的CSL_srioHwControl和CSL_intcHwControl就是实现这么目的。

另外SRIO还有一个中断速率控制寄存器,这个在每次中断发生后都需要向它写入一个数,即使不做中断速率控制也要写0。不然如果第二次中断标识产生了也进不了中断。调试的过程中发现,如果直接往中断速率控制寄存器中写0,程序就会反复进入这个中断服务函数。因此需要写一个较大的值,或者在中断服务函数外调用CSL_srioIntrRateCtrl。