TMS320C6455入门实践(七)

本系列文章链接

TMS320C6455入门实践(一)——编译CSL静态库

TMS320C6455入门实践(二)——中断相关

TMS320C6455入门实践(三)——PLL相关

TMS320C6455入门实践(四)——GPIO与定时器

TMS320C6455入门实践(五)——cmd链接脚本

TMS320C6455入门实践(六)——编写boot程序

TMS320C6455入门实践(七)——生成启动镜像

TMS320C6455入门实践(八)——Flash驱动与程序固化

TMS320C6455入门实践(九)——DDR上运行代码

TMS320C6455入门实践(十)——EDMA3相关

本文主要介绍hex6x工具的使用和实现“.out”文件转“.hex”,从而生成启动镜像,参考文档为:

SPRU186W - TMS320C6000 Assembly Language Tools v7.4 User’s Guide

hex6x工具的使用

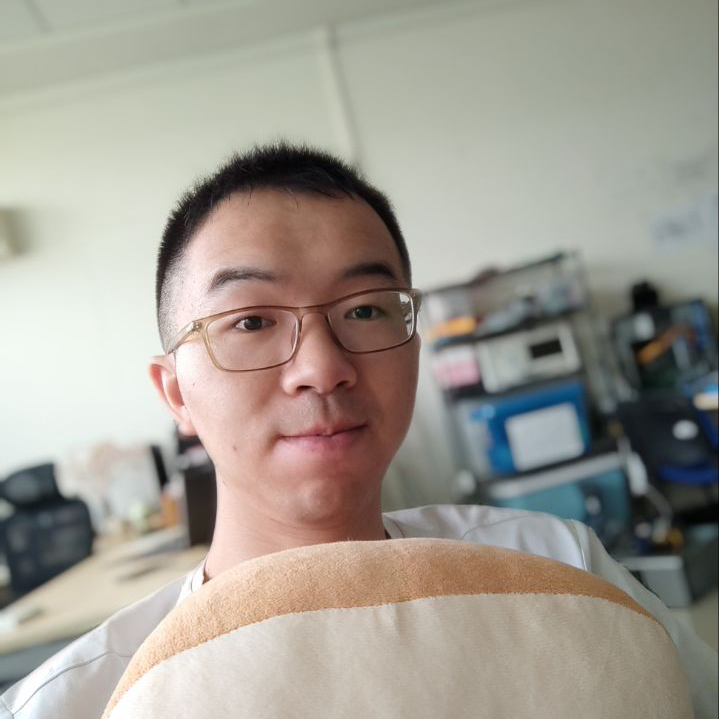

C6000 Compiler提供了一个“.out”文件转“.hex”文件的工具“hex6x.exe”,在编译器 ...

TMS320C6455入门实践(六)

本系列文章链接

TMS320C6455入门实践(一)——编译CSL静态库

TMS320C6455入门实践(二)——中断相关

TMS320C6455入门实践(三)——PLL相关

TMS320C6455入门实践(四)——GPIO与定时器

TMS320C6455入门实践(五)——cmd链接脚本

TMS320C6455入门实践(六)——编写boot程序

TMS320C6455入门实践(七)——生成启动镜像

TMS320C6455入门实践(八)——Flash驱动与程序固化

TMS320C6455入门实践(九)——DDR上运行代码

TMS320C6455入门实践(十)——EDMA3相关

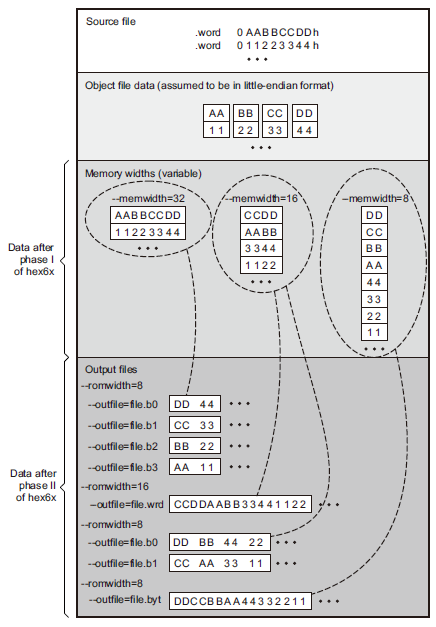

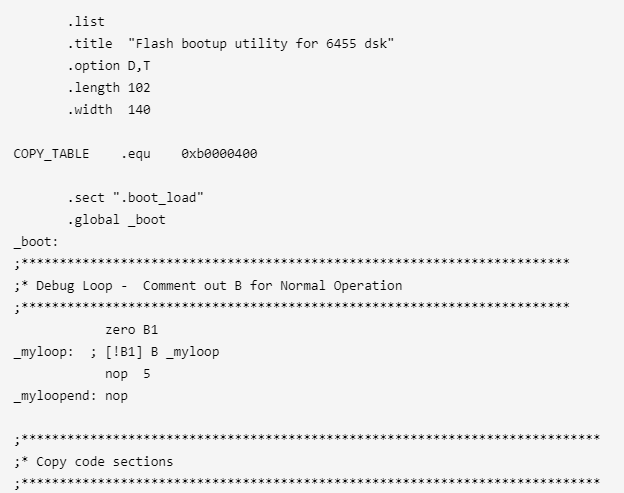

本文主要介绍C6455的二级boot的启动程序,参考文档为:

SPRUEC6G - TMS320C645x/C647x DSP Bootloader User’s Guide

SPRU732J - TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide

SPRU186W - TMS320C6000 As ...

TMS320C6455入门实践(五)

本系列文章链接

TMS320C6455入门实践(一)——编译CSL静态库

TMS320C6455入门实践(二)——中断相关

TMS320C6455入门实践(三)——PLL相关

TMS320C6455入门实践(四)——GPIO与定时器

TMS320C6455入门实践(五)——cmd链接脚本

TMS320C6455入门实践(六)——编写boot程序

TMS320C6455入门实践(七)——生成启动镜像

TMS320C6455入门实践(八)——Flash驱动与程序固化

TMS320C6455入门实践(九)——DDR上运行代码

TMS320C6455入门实践(十)——EDMA3相关

本文主要介绍C6000 Compiler的链接脚本相关的内容,参考文档为:

SPRU187U - TMS320C6000 Optimizing Compiler v7.4 User’s Guide

SPRU186W - TMS320C6000 Assembly Language Tools v7.4 User’s Guide

SPRA999A1 - Creating ...

TMS320C6455入门实践(四)

本系列文章链接

TMS320C6455入门实践(一)——编译CSL静态库

TMS320C6455入门实践(二)——中断相关

TMS320C6455入门实践(三)——PLL相关

TMS320C6455入门实践(四)——GPIO与定时器

TMS320C6455入门实践(五)——cmd链接脚本

TMS320C6455入门实践(六)——编写boot程序

TMS320C6455入门实践(七)——生成启动镜像

TMS320C6455入门实践(八)——Flash驱动与程序固化

TMS320C6455入门实践(九)——DDR上运行代码

TMS320C6455入门实践(十)——EDMA3相关

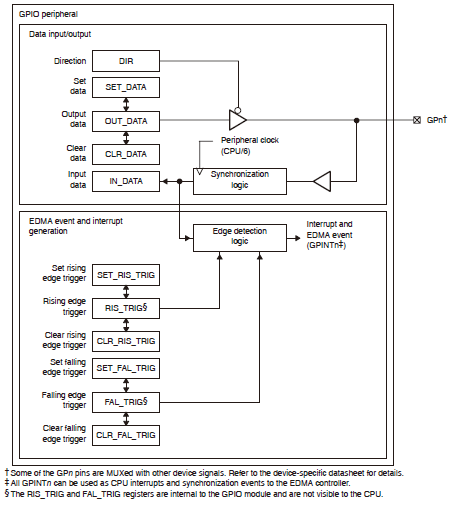

本文主要介绍TMS320C6455的GPIO和定时器相关的内容,参考文档为:

SPRS276M - TMS320C6455 Fixed-Point Digital Signal Processor

SPRU724A - TMS320C645x DSP General-Purpose Input/Output (GPIO) User’s Guide

SPRU968 - ...

TMS320C6455入门实践(三)

本系列文章链接

TMS320C6455入门实践(一)——编译CSL静态库

TMS320C6455入门实践(二)——中断相关

TMS320C6455入门实践(三)——PLL相关

TMS320C6455入门实践(四)——GPIO与定时器

TMS320C6455入门实践(五)——cmd链接脚本

TMS320C6455入门实践(六)——编写boot程序

TMS320C6455入门实践(七)——生成启动镜像

TMS320C6455入门实践(八)——Flash驱动与程序固化

TMS320C6455入门实践(九)——DDR上运行代码

TMS320C6455入门实践(十)——EDMA3相关

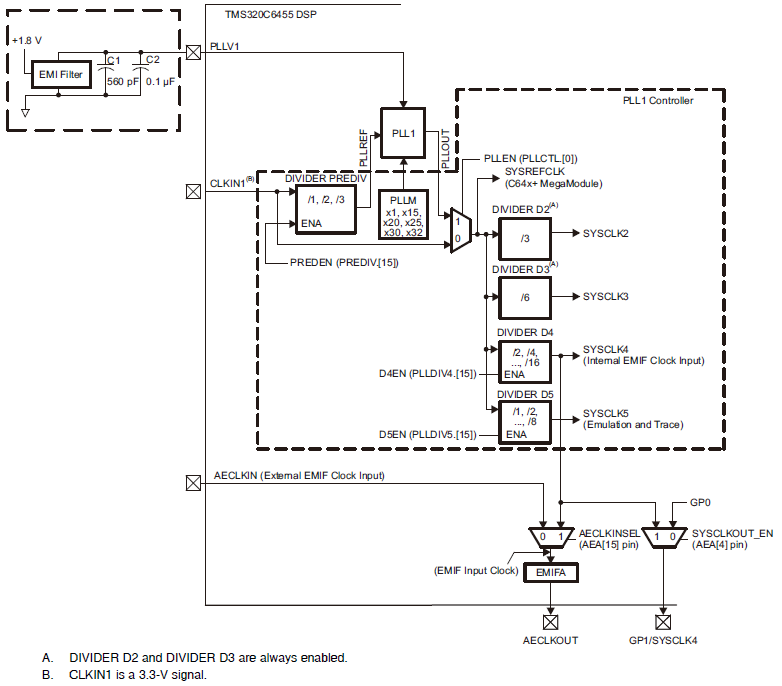

本文主要介绍TMS320C6455的时钟相关的内容,参考文档为:

SPRS276M - TMS320C6455 Fixed-Point Digital Signal Processor

SPRUE56 - TMS320C645x DSP Software-Programmable Phase-Locked Loop (PLL) Controller

C6455有 ...

TMS320C6455入门实践(二)

本系列文章链接

TMS320C6455入门实践(一)——编译CSL静态库

TMS320C6455入门实践(二)——中断相关

TMS320C6455入门实践(三)——PLL相关

TMS320C6455入门实践(四)——GPIO与定时器

TMS320C6455入门实践(五)——cmd链接脚本

TMS320C6455入门实践(六)——编写boot程序

TMS320C6455入门实践(七)——生成启动镜像

TMS320C6455入门实践(八)——Flash驱动与程序固化

TMS320C6455入门实践(九)——DDR上运行代码

TMS320C6455入门实践(十)——EDMA3相关

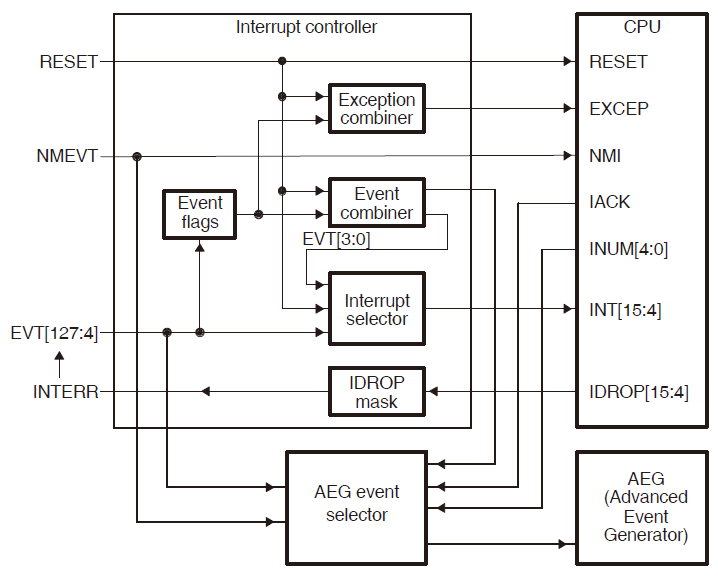

本文主要介绍TMS320C6455的中断相关的内容,主要的的参考文档有:

SPRS276M - TMS320C6455 Fixed-Point Digital Signal Processor

SPRU871 - TMS320C64x+ DSP Megamodule Reference Guide

SPRU732 - TMS320C64x/C64x+ DSP CPU ...

TMS320C6455入门实践(一)

本系列文章链接

TMS320C6455入门实践(一)——编译CSL静态库

TMS320C6455入门实践(二)——中断相关

TMS320C6455入门实践(三)——PLL相关

TMS320C6455入门实践(四)——GPIO与定时器

TMS320C6455入门实践(五)——cmd链接脚本

TMS320C6455入门实践(六)——编写boot程序

TMS320C6455入门实践(七)——生成启动镜像

TMS320C6455入门实践(八)——Flash驱动与程序固化

TMS320C6455入门实践(九)——DDR上运行代码

TMS320C6455入门实践(十)——EDMA3相关

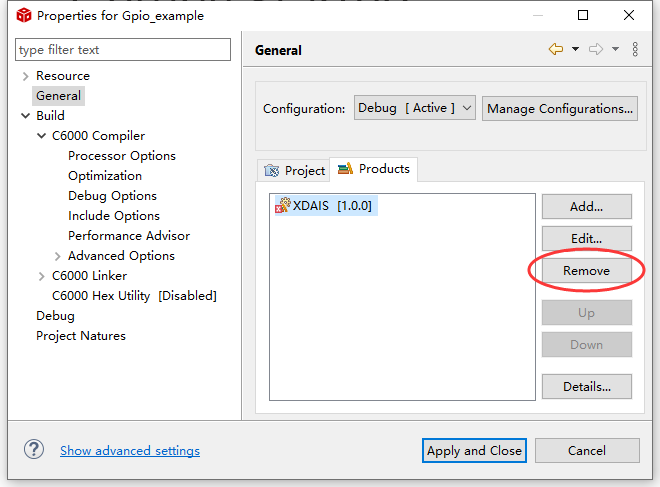

因为最近开始接手实验室的DSP开发相关的工作,所以也是刚开始学习使用相关的工具,顺便做了一些记录。本篇文章主要介绍一些初期的准备工作,包括CCS的版本选择、CSL静态库的编译,目的是能够无误地编译例程,为后续的开发做准备。

环境搭建

首先我们只需要有编译器就行。Code Composer Studio(CCS)是专门用于开发TI的处理器的集成开发环境(IDE), ...

基于Git和Tcl脚本的Vivado工程管理

参考文章:Version control for Vivado projects, 2014—— Jeff Johnson

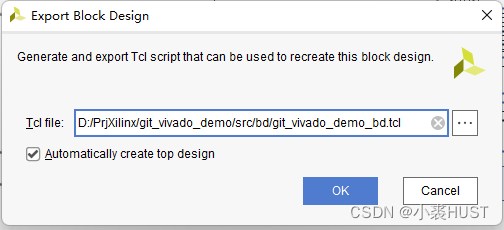

用Git做Vivado的版本控制,早在2014年就已经有人做了相关的工作。网上也有很多相关的文章介绍这个,但总感觉不是很方便。用Git做版本控制,主要就是对工程存档备份,在需要的时候方便回退版本。综合实现后的Vivado工程动辄上百兆,不方便直接用Git管理,工程中大部分都是Vivado生成的文件,所以用Tcl脚本重建工程是主流的选择。本文主要分享我的Vivado工程管理方法。

工程目录

project_name (工程名称)

ip_repo (存放用户自定义IP)

src

hdl (存放用户自己写的hdl代码)

constrs (存放用户自己写的约束文件)

bd (存放生成Block Design的Tcl脚本)

project_name (Vivado工程)

build.tcl (重建Vivado工程的Tcl脚本)

build.bat (双击开始重建工程)

.gitignore

看上面这个工程目录结构,可以看出来我这里的做法就是把所有用户 ...

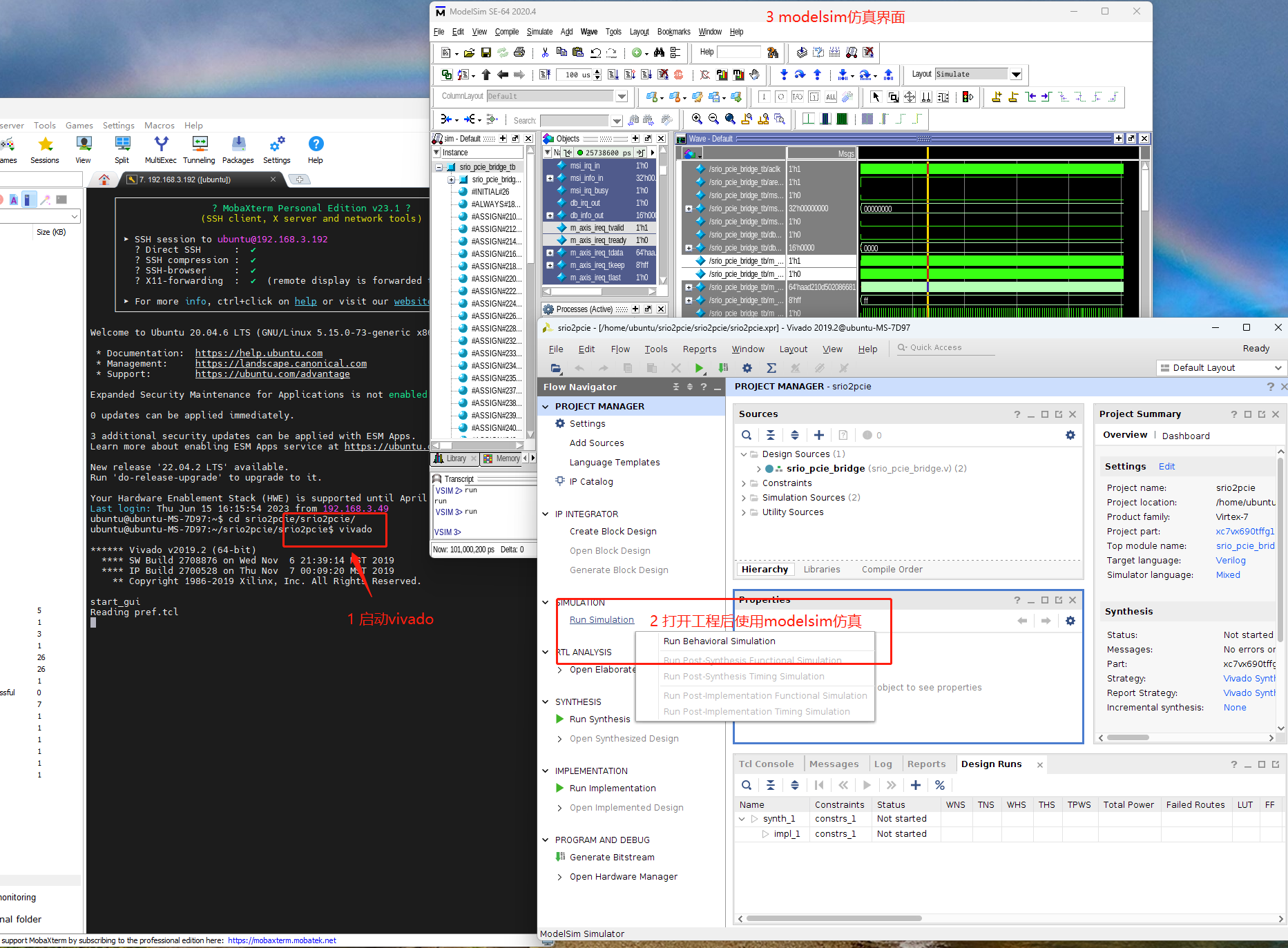

Vivado与Modelsim联合仿真

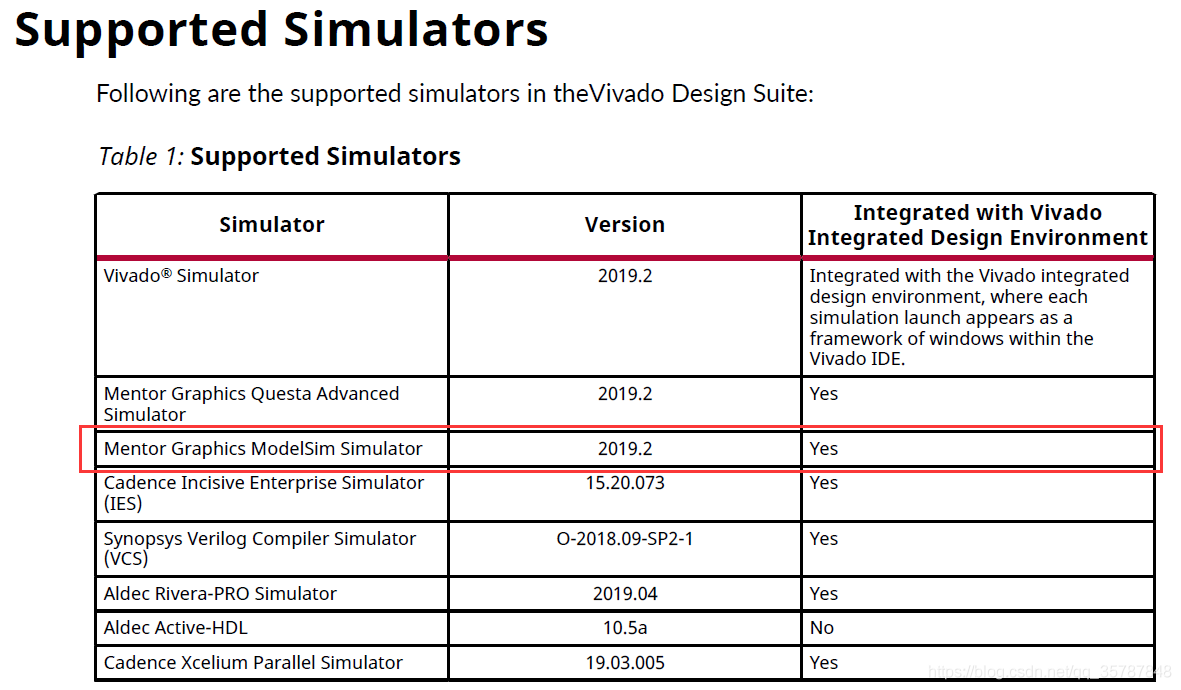

Vivado仿真器版本支持

首先查阅xilinx官方文档ug900(v2019.2),里面指出了vivado2019.2所支持的不同平台的仿真器版本。对于其他版本的vivado,应该也会在官方文档出给出,一定要注意查阅。

笔者采用的vivado版本为2019.2,可以从文档中看出,modelsim的版本也需要是对应的2019.2

编译Modelsim仿真库

关于编译仿真库,已经有很多其他博客给出了方法,不管是在vivado的图形化界面操作,或者输入tcl命令都非常方便。

但是笔者在编译仿真库的时候就一直出问题。一直出现“vlog-12110”的报错。查了很多资料,包括下图中的modelsim官方用户手册,都说modelsim10.7版本之后都不再使用-novopt的参数,按理说我不应该会遇到这个问题,我都已经是2019.2版本的modelsim了。

“vlog-12110”问题解决

该错误的主要问题是“-novopt”的参数一直在生效,但我并没有给出这样的参数,就很奇怪。

笔者详细查看了vivado给出的conpile_simlib编译后的log文件,可以看 ...

用于Vivado工程管理的Tcl语法学习

学习一样东西,很重要一点就是要知道学这个是为了什么。Tcl作为一种脚本语言,类似于Python,甚至可以用Tcl来简单地处理一些文件,只是不像Python有那么多库的支持。我也是昨天刚开始学习Tcl的语法,目的是为了用Tcl脚本重建Vivado工程,然后便于做版本管理。Tcl确实和很多人说的一样比较容易学,而且我觉得所有做FPGA开发的人应该都先学Tcl。

学习方式

学习一种语法我觉得最好的方法就是边看边自己敲代码练习,就像RUNOOB上的教程一样,每一条知识点都有一个例子,而且可以在线编辑。学习Tcl也可以采用类似的方法。我比较推崇使用VS Code,下面是我的学习方式。

下载安装

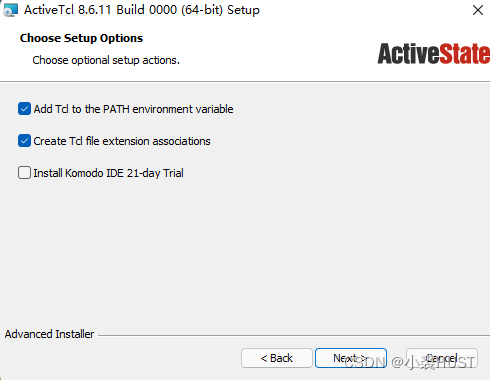

Active Tcl

Active Tcl类似于Tcl的一个发行版,在Tcl的官网上能够找到Tcl解释器的源码,Active Tcl在这个基础上又加了一些常用的Package。从官网下载之后再安装一下就可以了。安装的时候,

把Tcl的路径添加到PATH环境是必要的!

不建议把后缀为“.tcl”的文件和它绑定。就是下面图片里的第二个勾最好不要打,因为它会默认让Tcl脚本用Wish Appl ...